REFERENCE LEE ONLY

# LARGE SCALE SYSTEMS A STUDY OF COMPUTER ORGANIZATIONS FOR AIR TRAFFIC CONTROL APPLICATIONS

JOHN DUMANIAN

DAVID CLAPP

TRANSPORTATION SYSTEMS CENTER

55 BROADWAY

CAMBRIDGE, MA. 02142

JUNE 1971 TECHNICAL REPORT

Availability is Unlimited. Document may be Released To the National Technical Information Service, Springfield, Virginia 22151, for Sale to the Public.

Prepared for

FEDERAL AVIATION ADMINISTRATION WASHINGTON, D.C. 20546

|                                                                                                                                                                                                                                                                                                     |                    | 1201                       | MICAL REPORT 31                 | ANDARD TITLE PAGE |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------|---------------------------------|-------------------|

| Date Isc. The Tark                                                                                                                                                                                                                                                                                  | . Government Acces | sion No. 3. R              | ecipient's Catalog N            | о.                |

| - DOT-TSC-FAA-71-15                                                                                                                                                                                                                                                                                 |                    |                            |                                 |                   |

| 4. Title and Subtitle Large Sc. le Systems - A Stu                                                                                                                                                                                                                                                  | dy of Comput       |                            | eport Date<br>ne 15, 1971       |                   |

|                                                                                                                                                                                                                                                                                                     |                    |                            |                                 |                   |

| tions for Air Traffic Control Applications                                                                                                                                                                                                                                                          |                    | TC                         | erforming Organizatio<br>C      | on Code           |

| 7. Author(s)                                                                                                                                                                                                                                                                                        |                    |                            |                                 | - Parast Na       |

| John Dumanian & David Clapp                                                                                                                                                                                                                                                                         | _                  | 0. F                       | erforming Organizatio           |                   |

| 9. Performing Organization Name and Address DOT/Transportation Systems                                                                                                                                                                                                                              | Center             |                            | Work Unit No.<br>-03            |                   |

| Computer Technology Divisio                                                                                                                                                                                                                                                                         |                    | <b>+11</b>                 | Contract or Grant No            |                   |

| 55 Broadway                                                                                                                                                                                                                                                                                         | •••                | 1 '''                      | Contract of Grant No            |                   |

| Cambridge, MA 02142                                                                                                                                                                                                                                                                                 |                    | 13.                        | Type of Report and P            | eriod Covered     |

| 12. Sponsoring Agency Name and Address                                                                                                                                                                                                                                                              |                    |                            |                                 |                   |

| FAA-SRDS-RD-123                                                                                                                                                                                                                                                                                     | G 11               | Te                         | chnical Repo                    | rt                |

| FOB 10A, 800 Independence A                                                                                                                                                                                                                                                                         |                    |                            |                                 |                   |

| Washington, D.C. 20546                                                                                                                                                                                                                                                                              | 2011               |                            | Sponsoring Agency C<br>A RD-123 | ode               |

| 15. Supplementary Notes                                                                                                                                                                                                                                                                             |                    |                            |                                 |                   |

|                                                                                                                                                                                                                                                                                                     |                    |                            |                                 |                   |

|                                                                                                                                                                                                                                                                                                     |                    |                            | *                               | £ 0               |

| 16. Abstract                                                                                                                                                                                                                                                                                        |                    |                            |                                 |                   |

| Based on current sizing estimates and tracking algorithms, some computer organizations applicable to future air traffic control computing systems are described and assessed. Hardware and software problem areas are defined and solutions are outlined. System evaluation criteria are presented. |                    |                            |                                 |                   |

| Section 1: delineates the objectives and approach, and furnishes definitions                                                                                                                                                                                                                        |                    |                            | initions                        |                   |

| of computer hardware and software;  Section 2: presents the ATC data processing requirements: the anticipated traffic, the computer processing rates, and the methods for                                                                                                                           |                    |                            | ipated ·                        |                   |

| <pre>analyzing computer performance; Section 3: describes current computing systems with capabilities for usage</pre>                                                                                                                                                                               |                    |                            | usage                           |                   |

| in near future                                                                                                                                                                                                                                                                                      | ATC applicat       | TOUS!                      |                                 |                   |

| Section 4: denotes the algorithm programs;                                                                                                                                                                                                                                                          | gorithms which     | h are to be used i         | in the projec                   | eted ATC          |

| Section 5: sums up the future prospects in ATC data processing, assesses the risks and points out some future work efforts.                                                                                                                                                                         |                    |                            |                                 |                   |

| the risks and points out some rature work circles.                                                                                                                                                                                                                                                  |                    |                            |                                 |                   |

|                                                                                                                                                                                                                                                                                                     |                    |                            |                                 |                   |

| _                                                                                                                                                                                                                                                                                                   | 3                  |                            |                                 |                   |

|                                                                                                                                                                                                                                                                                                     |                    |                            |                                 |                   |

|                                                                                                                                                                                                                                                                                                     | neo                |                            |                                 |                   |

| 17. Key Words                                                                                                                                                                                                                                                                                       |                    | 18. Distribution Statement | 1                               |                   |

| Computors                                                                                                                                                                                                                                                                                           |                    |                            |                                 | ie .              |

| Computers                                                                                                                                                                                                                                                                                           | _                  |                            |                                 |                   |

| NAS Stage A Data Processing                                                                                                                                                                                                                                                                         | g                  |                            |                                 |                   |

| ARTS III Data Processing                                                                                                                                                                                                                                                                            |                    |                            |                                 |                   |

| ×                                                                                                                                                                                                                                                                                                   | ×                  |                            |                                 |                   |

| 19. Security Classif. (of this report)                                                                                                                                                                                                                                                              | 20. Security Class | iif, (of this page)        | 21- No. of Pages                | 22. Price         |

|                                                                                                                                                                                                                                                                                                     | 1                  |                            | 152                             |                   |

| Unclassified                                                                                                                                                                                                                                                                                        | Unclassi           | ted                        | 172                             |                   |

# TABLE OF CONTENTS

| SECTION                                                                                                                                                                                                                                                                                                                                         | PAGE                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1.0 OBJECTIVES AND DEFINITIONS                                                                                                                                                                                                                                                                                                                  | 1                           |

| 1.1 Introduction                                                                                                                                                                                                                                                                                                                                |                             |

| 2.0 ATC DATA PROCESSING REQUIREMENTS                                                                                                                                                                                                                                                                                                            | 33                          |

| 2.0 Introduction                                                                                                                                                                                                                                                                                                                                | r 1980 33<br>37<br>stems 43 |

| 3.0 SURVEY OF SYSTEMS AND TECHNIQUES                                                                                                                                                                                                                                                                                                            | 56 ft.                      |

| 3.1 Introduction 3.2 Comparisons of Structures 3.3 IBM 9020 Multiprocessor 3.4 ARTS III Multiprocessor 3.5 Current ATC Executive Systems 3.6 T.I. Advanced Scientific Computer 3.7 Goodyear Associative Processor 3.8 Two New Associative Processor 3.9 PEPE, Parallel Element Processing Ensembl 3.10 CDC-STAR 3.11 ILLIAC IV 3.12 Some Others |                             |

| 4.0 ATC ALGORITHMS                                                                                                                                                                                                                                                                                                                              | 141 /5/)                    |

|                                                                                                                                                                                                                                                                                                                                                 | 0 1500                      |

## ADVANCED AIR TRAFFIC CONTROL COMPUTER SYSTEMS

#### 1. OBJECTIVES AND DEFINITIONS

### 1.1 INTRODUCTION

The study effort under FA-03-01, Large Scale Systems, has resulted in this Final Report describing large computing systems and software anticipated for the early eighties. Features expected to be found in large real-time computers of that era which could handle the large ATC data processing loads forecasted are emphasized. Software advances which will affect the situation at that time are also included. Extrapolations are made from current computer hardware, which is described in detail. Criteria are developed for evaluating the future systems.

## 1.2 OBJECTIVES AND APPROACH

The objective of this report is to provide information on hardware/software systems applicable to fourth generation ATC data processing systems. The approach is through studies of large real-time computers, ATC computations and algorithms, and criteria for evaluating large-scale systems.

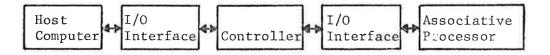

Following a discussion of ATC data processing requirements in Section 2, a detailed presentation is made in Section 3 of the significant features of a number of commercial, military and experimental machines having capabilities responding to future ATC needs. Computers described are the IBM 9020, 360/195, 370/165, ARTS III, CDC 7600, STAR, TI Advanced Scientific Computer, PEPE, the Goodyear Associative Processor and ILLIAC IV. Correlation and tracking algorithms are reviewed and compared in Section 4 with some discussion of possible improvements.

It is hoped that the repertory of techniques presented here will be useful in defining new systems to meet future ATC requirements as they evolve.

The remainder of Section 1 is devoted to brief definitions of some of the terms used in present-day descriptions of computation systems.

## 1.3 COMPUTER HARDWARE

The major components of computers will be reviewed. These include memories, processors, I/O processors, I/O controllers, and I/O devices.

1.3.1 Memory. Memory can be broadly divided into two classes:

main (memory) storage characterized by high speed, and

secondary (auxiliary) storage characterized by large

storage capacity.

Main storage is a general-purpose, addressable, read/write storage medium used to hold programs and data. It may be thought of as an array of N, M-bit, storage registers. Information in a given register may be accessed by specifying the address or location of the information in the array. The contents of one of the m-bit registers is the basic unit of storage. Main storage is random access, i.e., the time required to access a basic unit of information is independent of the location of the information in the array. Each processor is provided a dedicated processor-to-memory data path, independent of I/O, to access information in main storage.

Random access memories are either <a href="read-only">read-write</a> (RWM). The information in a ROM is inserted at the time the memory is manufactured. It can only be changed by physically altering the memory. For equivalent size and speed, read-only memories are usually lower in cost when mass produced in identical patterns, than read-write memories. Read-write memories which are electrically alterable, sometimes are operated as ROM's in computer systems.

Memories are considered volatile if they lose information during lapses of power, non-volatile if they do not.

Memories which use magnetic storage elements (cores, plated wire, etc.) are usually non-volatile and memories which use active storage elements (semiconductors) are usually volatile.

Non-volatile memories can be further classified as either destructive read-out (DRO) or non-destructive read-out (NDRO) memories. When information is read from a location in a DRO memory the information stored in that location is destroyed by the read-out process. To preserve the stored information, each read-out operation is normally followed by a restore (write-back) operation. This extra operation lengthens the cycle time of the memory.

Core memories operate in the DRO mode, semiconductor memories in the NDRO mode, and plated-wire memories in both modes. Computer main memories have cycle times between 1/2 and 10 microseconds, and access times between 1/4 and 5 microseconds. The size of these memories is between  $10^4$  and  $10^8$  bits. Ferrite core memories still rule as the chief form of computer main memory.

Recently, IBM<sup>1</sup> has employed semiconductor memories as high-speed main storage buffers. The largest of these has a 32K byte capacity and a 54 nano-second cycle time. Plated wire memories have found use in military computer systems where severe environmental constraints limit the other technologies.

Secondary storage made up of magnetic disks, drums, and tape, are of large capacity, have long access times and are accessed via input-output instructions. Data on secondary storage devices are transferred to main storage, a block of words at a time. Information is stored in volumes. A volume is a unit of auxiliary storage accessible to a single read-write mechanism. A dismounted volume is referred to as external storage.

A sequential-access secondary storage device (magnetic tape) accesses data by linearly positioning the volume relative to the read-write mechanism, i.e., moving the volume forward or backward until the desired physical record is found. The time required to access a record is therefore dependent on the position of the desired record relative to the record presently under the read-write mechanism.

Direct access secondary storage devices (disk, drum, etc.) allow random access to data stored on a volume. Information is accessed by referencing its location in the volume. In this respect, direct access devices are similar to main storage. The time required to access information may or may not be dependent on the location of the information. For example, the time required to access information on a disk includes seek time, the time required to position the read-write mechanism over the correct disk track, and rotational delay--the time required for the information on a track to rotate to a position under the read-write mechanism.

<sup>1</sup> IBM Systems Journal, Vol. 7, No. 1, 1968, Structual Aspects of the System/360 Model 85 II The Cache by J.S. Liptag.

Secondary storage devices may be characterized by three parameters. They are: access time--the time required to position the first basic unit of desired information under the read-write mechanism; transfer rate--the rate in bits per second at which information can be read/written from/into a volume once access has been obtained; storage capacity--the number of bits of information that can be stored on a volume.

The characteristics of present day secondary storage devices are listed below.

| DEVICE        | CAPACITY      | ACCESS TIME | TRANSFER RATE    |

|---------------|---------------|-------------|------------------|

| Magnetic Tape | 50-400 M bit  | 10 MS-3 MIN | 8K-2M bit/sec    |

| Disk          | 10-6000 M bit | 20-500 MS   | 0.5-16 M bit/sec |

| Drum          | 1-150 M bit   | 8-60 MS     | 2K-20M bit/sec   |

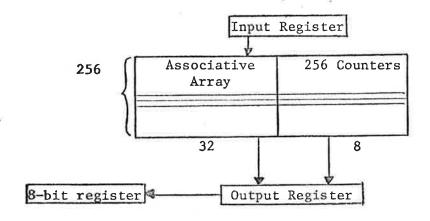

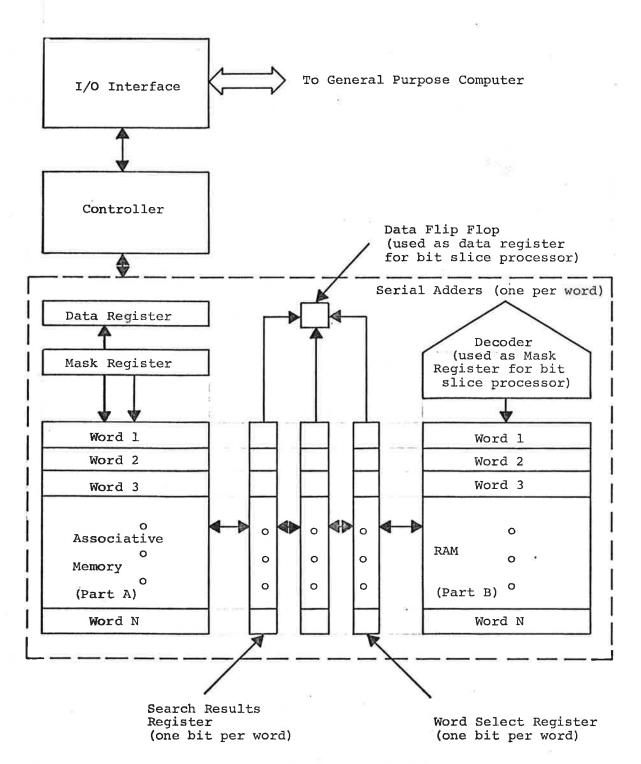

In addition to main storage and secondary storage, a third form of storage known as an associative (content addressable) memory has recently come into use. Information in an associative memory is accessed by content rather than by address. Each word which is loaded into an associative memory contains one or more keys which will be used to access the information stored in the remainder of the word.

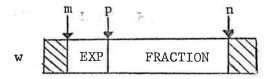

## ASSOCIATIVE MEMORY DATA WORD

To access a data word the key is presented to the associative memory. The memory then replies by providing the data word that matches the key. If two or more items in the memory can have the same key then the associative memory must perform some form of multiple match resolution so that only one reply results. Associative memories are very useful when table lookup or fast searches must be carried out.

The purpose of an associative memory is to provide an aid to a computer with its powerful simultaneous parallel search capability. The associative processor is a further extension to the associative memory in that a limited (serial) arithmetic capability is added. There are several recent applications of both associative memories and associative processors.  $^{6-12}$

The basic cell of an associative array is a flip-flop and a match circuit. The cells are arranged in the array as they would be in a normally addressed memory array, N bits per word, M words long, but with columnar linkages in each bit column so that each bit of an argument word can be matched with the equivalent bit in each of the memory words. Where the totality of the argument bits match the memory word bits, a match condition is met and a flag is raised. It then remains for a multiple match resolver to home in on one. To express this mathematically and symbolically, it can be shown that:

given word  $\mathbf{A}_1,\dots\mathbf{A}_N,$  an N bit word to be matched, from a memory  $\mathbf{B}_{MN}$

| B <sub>11</sub> | B <sub>1N</sub> |

|-----------------|-----------------|

|                 |                 |

| R               | Въох            |

| 1 PM1           | DMM             |

Totality M N

of

$$=\sum_{j=1}^{N} \prod_{i=1}^{N} A_i \oplus B_{ij}^{\dagger}$$

Words

Multiple

Totality of Matched Words→ Match → one matched word

Resolver

Plated wire memories were used to fabricate associative memories. Now semiconductor chips are being made, but they are expensive. They are 20 times the cost of ordinary semiconductor memory chips. However, the price is due to come down shortly and the use of them is spreading. It will not be long before associative memories and associative processors become integral parts of a computer.

Processors. The processor units of a computer are those elements which decode and execute the instructions of a program. Processors can be classified as general-purpose processors, which are capable of solving a large class of problems, or special-purpose processors which are capable of solving a restricted class of problems. A general-purpose processor can be thought of as several special-purpose processors operating under common control. Processors contain one or more of the following units: memory access units (MAU), computational or arithmetic and logic (ALU), input/output unit (IOAU), control or instruction unit (CU). The number of units of each type used and the number of data paths interconnecting the

units are important in determining the instruction execution rate of processors. The control unit decodes instructions and issues the micro-orders (control pulses) needed to cause execution of the decoded instructions by the processor subunits. The micro-orders cause the processor to fetch the next program instruction from memory, decode its operation code, fetch any required operands, carry out the operation, and store the result in the proper location. Thus, the control unit in conjunction with the processor automatically sequences through the program in main storage. A processor may have a mixture of general-purpose computational units and special-purpose units. Special-purpose units are used to decrease the time required to perform certain operations, e.g., complex arithmetic operations. memory access unit and the I/O access unit handle all processor-to-memory and processor-to-I/O device communications.

Fast processors are composed of special-purpose execution and control elements that can be operated concurrently. Concurrent operation is achieved by providing each concurrent unit with its own local storage (hardware registers) and a local control unit. Operation of the various concurrent units is synchronized by the main control unit of the processor.

There is a large disparity between processor computational speed and I/O device operating speed. Therefore, most processors contain one or more special-purpose subunits known as I/O processors or channels. These carry on I/O operations in parallel with processor computations. They do this by executing I/O programs which are setup in advance by the computation element of the processor. On some computer systems with more than one processor, a complete general-purpose computer is dedicated to the task of performing I/O operations. When it is used in this fashion, the general-purpose computer is called an I/O processor.

1.3.3 Processor Organizations. In this section several processor organizations will be discussed.

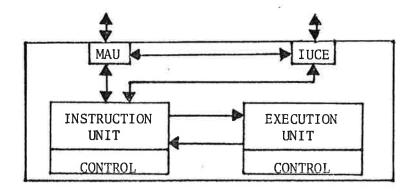

The organization of the <u>conventional processor</u> is presented in Figure 1. The processor contains a memory access unit (MAU), input/output access unit (IOAU) arithmetic & logic unit (ALU), and a control unit (CU).

DATA PATH

---- CONTROL PATH

## CONVENTIONAL PROCESSOR ORGANIZATION

## FIGURE 1

It processes program instructions in a sequential manner. A typical sequence of operations required for processing an instruction proceeds as follows:

- 1. The address of the next instruction to be fetched is generated from information in the processor's control unit at the time of the last instruction executed.

- 2. The instruction is fetched from memory and placed in the control unit.

- 3. When the instruction arrives at the control unit, it is decoded. If an operand is required, its memory address is resolved.

- 4. The operand is fetched from memory and placed in the ALU.

- 5. The result of the operation is stored in the proper location, either in main memory or in a hardware register.

- 6. Steps one thru five are repeated.

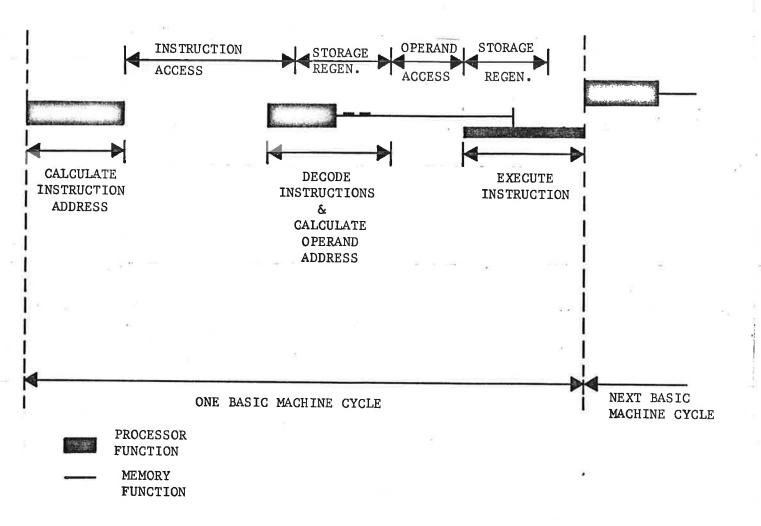

Steps 1 through 5 represent the basic cycle of the machine. A timing diagram which graphically depicts both memory and processor functions during two basic processor cycles of operation is shown in Figure 2.

TIMING DIAGRAM FOR PROCESSOR BASIC CYCLE OF OPERATION

FIGURE 2

¥ TIME

ILLUSTRATION OF CONCURRENCY AMONG SUCCESSIVE INSTRUCTIONS

FIGURE 3

As can be seen, an appreciable portion of the basic cycle is spent waiting for instructions, operands, and results from operations. Two bottlenecks to more efficient utilization of processors resources are apparent from this diagram. They are the memory-to-processor data rate and the long execution time of the instructions.

The concurrent processor uses organizational techniques to eliminate these bottlenecks. The concurrent processor allows several instructions to be in various stages of processing within the processor at the same time. A timing diagram which illustrates the concurrency among successive instructions is shown in Figure 3. As can be seen by comparison with Figure 2, the effective instruction execution rate has been increased many times at the cost of some additional hardware.

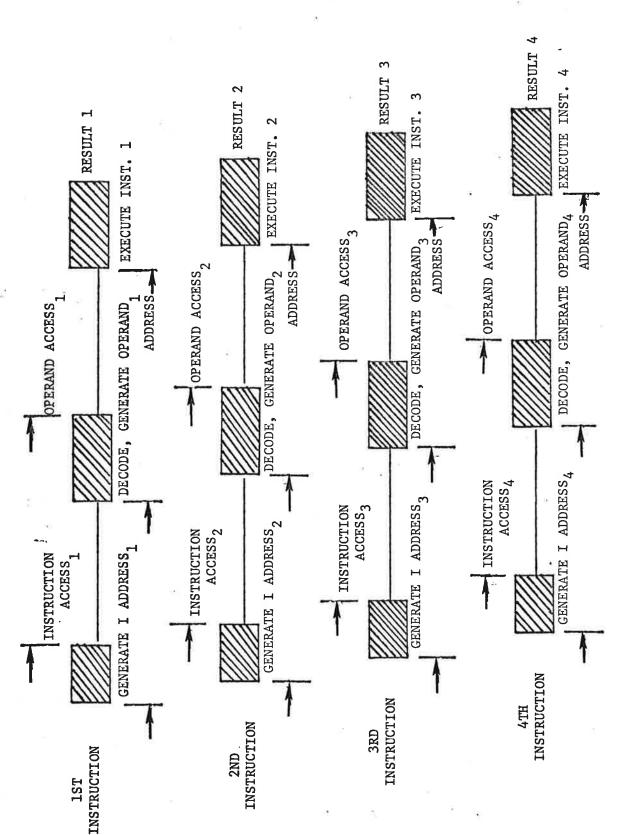

The organizational techniques used to achieve concurrency are: memory interleaving, instruction fetch-execution overlap, execution concurrency and pipelining. Memory interleaving (see Figure 4) is a technique used to increase the effective data transfer rate between main storage and the processor.

INTERLEAVED MEMORY ADDRESSING STRUCTURE

FIGURE 4

It is implemented by splitting main storage into several independent modules and arranging the addressing structure so that n successive words are fetched from n different modules in one memory cycle. Due to limitations on hardware registers, the n words from the n different modules are stored in registers during submultiples of the memory cycle. A delay of one memory cycle is still incurred when fetching and storing information. But by assigning successively used instructions and data to successive storage locations (i.e., different modules) whenever possible, advantage may be taken of the memory interleaving. If program branches are infrequent, then the processor-to-memory data transfer rate can be increased by a factor that approaches the degree of memory interleaving. The degree (or amount) of interleaving required for a certain amount of processor concurrency is dependent on the memory cycle time, processor request rate and the desired effective storage access time.

Within the processor, the natural way to increase instruction execution rate is to overlap instruction fetching and execution. This is accomplished by partitioning the processor (see Figure 5) so that instruction fetching, decoding and operand fetching are carried out by one unit, and actual execution by a second unit. Each has its own local control unit so that it can operate in an independent fashion. The units operate as follows. The instruction unit prepares an instruction for execution. It fetches any required operands from memory. When the necessary preprocessing is complete, the instruction unit tests the execution unit to see if it is busy. If the execution unit is free, the instruction unit tells it to begin processing the instruction that was just prepared. Immediately after acceptance of the command the instruction unit starts preparation of the next instruction. Both units are now processing concurrently. If the instruction unit finishes preparation of the next instruction before the execution unit completes its processing, it must wait. If the execution unit finishes first, then the instruction unit can initiate the execution of the next instruction and start the preparation of another instruction. Whenever a branch instruction is encountered, the instruction unit assumes the branch will not be taken and continues to fetch instructions from the same sequence in storage. If the branch is taken, the instruction unit discards the now-irrelevant data and initiates processing at the branch location.

PROCESSOR WITH FETCH-EXECUTION OVERLAP

#### FIGURE 5

The technique just discussed is known as a single instruction overlap. Sometimes, this is not enough. The techniques of pipelining, internal buffering and execution concurrency can be used to overcome the limitations imposed on the inability of the instruction unit and execution unit to perform at a desired rate.

Execution concurrency is a technique used to increase the processing capability of the execution unit. To achieve it, the execution unit is divided into several special-purpose processing elements, etch capable of executing a subset of the processors total instruction set. Each element is provided with its own local unit so it can operate in an independent manner. Operations in the individual elements are initiated by commands received from the instruction unit. The synchronism required to insure that instructions are executed in the correct sequence is provided by tags and interlocks within the various units and the instruction unit.

Since some elements are designed to execute special instructions, execution concurrency, i.e., several instructions being executed at the same time, can be achieved when a proper instruction mix is applied. For instructions which require long execution times, a special execution unit is implemented; and to balance the total operation, a certain number of common execution units according to the average mix of instructions are used.

The ability to process more than one instruction at a time in the instruction unit and in individual execution elements can be achieved by using pipeline techniques.

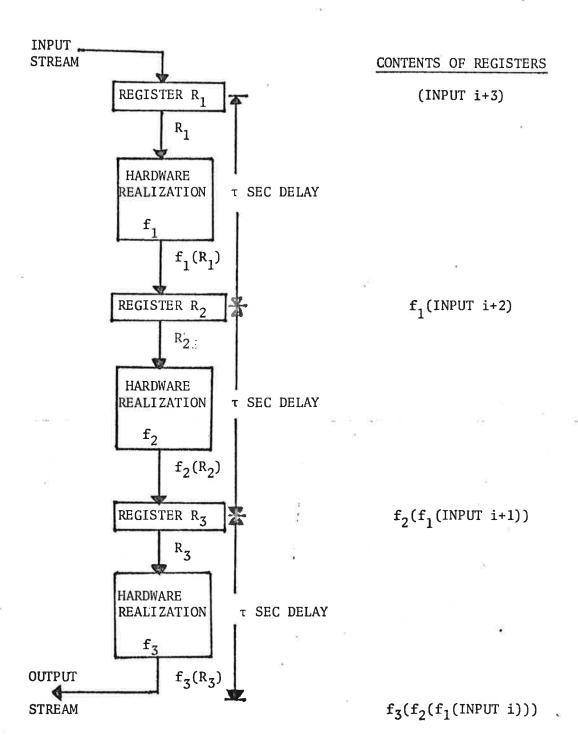

To implement a pipeline execution element or instruction unit (see Figure 6), the function to be performed by the unit, must be broken into several processing steps,  $f_1$ ,  $f_2$ ,  $f_3$ , that are hardware implementable. Temporary storage registers  $R_1$ ,  $R_2$ ,  $R_3$  are then installed between the hardware units that perform the between-step processing. Processing proceeds from time,  $t = t_0$ , when the first instruction and data set is loaded into register  $R_{ extsf{1}}$  . At time  $T = t_0 + \tau$ , where  $\tau$  equals the pipeline interstage delay, the second instruction and data is loaded into  $R_1$ and the output result from the first processing step,  $f_1(R_1)$  is baded into register  $R_2$ . At time  $T = t_0 + 2\tau$ , a third instruction and data set is loaded into register  $\mathbf{R}_1$  and  $\mathbf{f}_1(\mathbf{R}_1)$  resulting from the second instruction and data set is loaded into  $R_2$  and  $f_2(R_2)$  of the first instruction set is loaded into register Rz. Three instructions are now ar various stages of processing within the pipeline unit. At time  $t = t_0 + 3\tau$ , a fourth instruction set is loaded into register  $R_1$  and  $f_1(R_1)$  of the third instruction set is loaded into register R2 and  $f_2(R_2)$  resulting from second instruction set is loaded into  $R_3$  and the final result of the first instruction  $f_0 = f_3(R_3)$ is made available at the output of the pipeline unit. The pipeline is now full and as long as a steady stream of instruction and data are available, results will come out of the pipeline at intervals of  $\tau$  seconds.

In the example presented, a three-stage pipeline unit, t would be approximately one-third the time required to process an instruction and data in a non-pipelined unit. This means that once the startup transient has died away, a pipeline processing element can process instructions and data at approximately N times the rate of a nonpipeline unit, where N equals the number of stages in the pipeline. A processor which uses pipeline techniques to achieve execution concurrency is called a pipeline processor.

When using any of the previously mentioned techniques, internal buffering in the form of high-speed registers, is usually required to smooth the flow of data and instructions between the various processor elements. The number of stages of buffering required depends on the organization of a processor, the capability of the instruction unit, the desired rate of instruction execution, and the techniques used to preserve the proper order between instructions.

Processors which use any or all of the above techniques are called highly serial processors since they process instructions in a sequential manner.

FUNCTIONAL BLOCK DIAGRAM OF A PIPELINE PROCESSING UNIT FIGURE 6

The Control Unit (CU) in Figure 1 decodes machine-language instructions and interprets them at the circuit level in terms of the data transfers and control signals required to execute the instructions. In many systems a separate hard-wired logic circuit is used to implement each instruction in the machine language. Microprogramming can be used to simplify the design of the CU, however, and is finding increasing use in modern machines. The essential idea is to use a stored program of microinstructions, each of which sets gates to define a path along which data or control signals will travel. Microprogramming not only reduces the amount of circuitry required for the CU but also makes it economical to provide a richer instruction set at the machine-language level.

A completely microprogrammed instruction set also makes it possible for one computer to emulate another, i.e., for one computer to perform calculations and logical operations according to the system architecture and instruction set of some entirely different type of computer.

Microprogramming may be implemented using read-only storage, or writable storage. In the latter case changes or additions to the microcode are quickly made, whereas in the read-only case changes involve mechanical replacement of storage units. If a volatile semiconductor medium is used for high speed, it must be reloaded each time the power is turned on, as e.g., in the IBM 370/135 and 145 which use a special console disk unit for this purpose.

I/O Channels and Processors. Early computers carried on I/O operations by having the central processor execute the I/O instructions. Whenever I/O instructions were encountered, the processors would become dedicated to the I/O task which would mean operating at a reduced rate. Handling the I/O greatly reduced the effective speed of processor operation.

To overcome this, computers were adapted with hardware units known as channels which allowed I/O operations, once initiated, to proceed in parallel with processor computation. In the simplest form, a channel is capable of executing a single I/O instruction transferred to it from the central processor. More sophisticated channels are capable of executing strings of instructions which are stored in memory. Some computers even have small dedicated processors known as I/O, peripheral, or satellite processors which carry out the processor-to-memory data transfers.

Most medium and large-scale computers have one or more channels that carry on data transfers under the control of a channel program which is executed independently of the central processor program. The central processor exercises control over the operation of the channels. To do this, it has facilities (hardware and software) for initiating the operation of a channel and for the receiving of completion signals (interrupts) from the channel. The processor on receipt of the interrupt stops processing and analyzes the cause of the interrupt. The cause of an I/O interrupt may be due to a normal task completion or due to some form of error of hardware failure. If the interrupt was a normal termination then both the data and the channel become available for use by the processor.

The instruction executed by the channels are of the following types: data transfer commands, sense commands, control commands, change of sequence commands. Data transfer commands are read or write commands which cause data to be transferred between the I/O devices and main storage. These commands specify where in memory the data is to be placed and the amount of information to be transferred. Sense commands carry information into main storage concerning the status of a channel. Control commands specify device operations such as backspace, rewind tape, advance paper, etc. Change of sequence commands specify the location in main storage from which the next instruction is to be fetched. Both conditional and unconditional branches are handled in this manner. Channels are usually one of two types--selector or multiplexer.

A selector channel is a type of channel which is capable of carrying on data transfers to one device at a time on a dedicated basis -- several devices may be connected to a selector channel, but only one may be active during a given channel program. Transfers are initiated by the central processor, which supplied the address of the first instruction of the channel program that will control the transfer and the identification of the device that will be used for the transfer. The channel then takes control and executes the channel program concurrent with CPU processing. When the program is completed, the channel notifies the CPU so that another I/O operation can be scheduled. A selector channel is said to operate in a burst mode because the channel is tied up for the entire duration of the transfer including the time spent waiting for the device to complete its mechanical operation.

A multiplexer channel is capable of carrying on data transfers with several devices at seemingly the same time, in a time multiplexed basis. Low data rate devices then share the same channel facilities. Information is transferred to individual devices by broadcasting, simultaneously over the same set of data lines, the data and the identification of the device involved. Associated with each device is a dedicated group of storage locations for the storage of all information required to maintain an independent transfer to a device. The stored information consists of the address of the next channel instruction, channel status information, and the channel instruction presently in process, as well as information such as the base address of the data buffer in main storage, its size, and the operation being performed by the instruction. information is updated by the channel each time a new instruction is executed or a data transfer to the device takes place. Transfers to the individual devices are scheduled automatically by the channel as the devices become available to accept or transmit data. Programs are initiated and terminated in the same manner as on a selector channel except the multiplexer channel continues to process any remaining active channel programs after notifying the central processor of completion of one channel program.

Satellite computers and I/O processors operate in a manner similar to a multiplexer channel except that the processor can also perform editing and formatting functions on the data before it is transferred. More flexible scheduling is also possible.

- 1.3.5 I/O Controllers. I/O controllers are special-purpose devices which interpret the commands broadcast by the I/O channels. They are located between the I/O devices and the channel to which they are connected. They provide the timing and sequencing signals needed to make the I/O devices carry out the operations specified by the channel commands.

- 1.3.6 I/O Devices. Into the category of I/O devices fall drums, disks, card readers, large core memories, etc., and transducers of various types. They are peripheral to computers and are connected to them via I/O channels. The common characteristics of these devices are response times, low data transfer rates, and varied control sequences.

## 1.4 SYSTEM ORGANIZATION

1.4.1 System Configurations. There are a large number of system configurations (organizations) currently in use. Among these appear four major configurations.

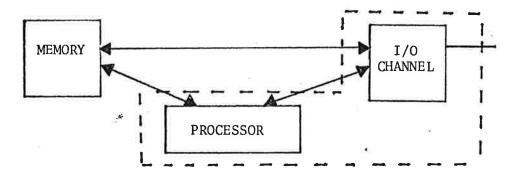

The simplest and most often used is the <u>single computer</u> or <u>uni-processor</u> system which is shown in Figure 7. The processor is connected to memory and to the I/O channel; the memory communicates with the processor and the I/O channel. Connections to the I/O devices are not shown. The processing capability of this configuration is limited by the capability of the single processor in the system.

UNI-PROCESSOR CONFIGURATION

Figure 7

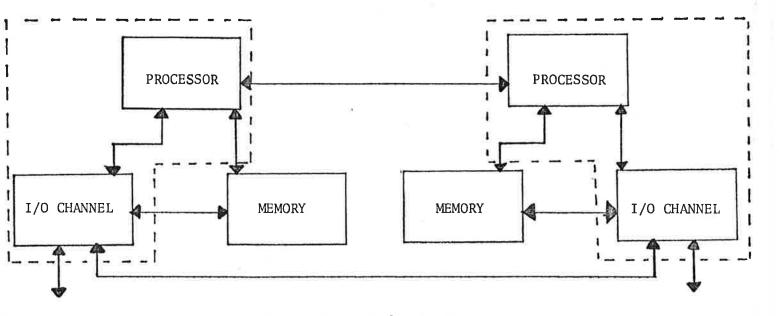

To increase processing capability, computer manufacturers went to the <u>multicomputer</u> system configuration (see Figure 8). In this system, the processors are often of different size. Normally, the smaller of the two carries on the I/O and housekeeping functions while the larger acts as the primary computation element of the system. The two processors are linked by processor-to-processor

MULTICOMPUTER CONFIGURATION

Figure 8

and channel-to-channel data links. The channel-to-channel link is used to transfer information between the main storage units of the two computers. I/O devices may also be shared via this link. The processor-to-processor data link permits one processor to notify the other that it is wanted to do something. It is most often used to setup storage data transfers.

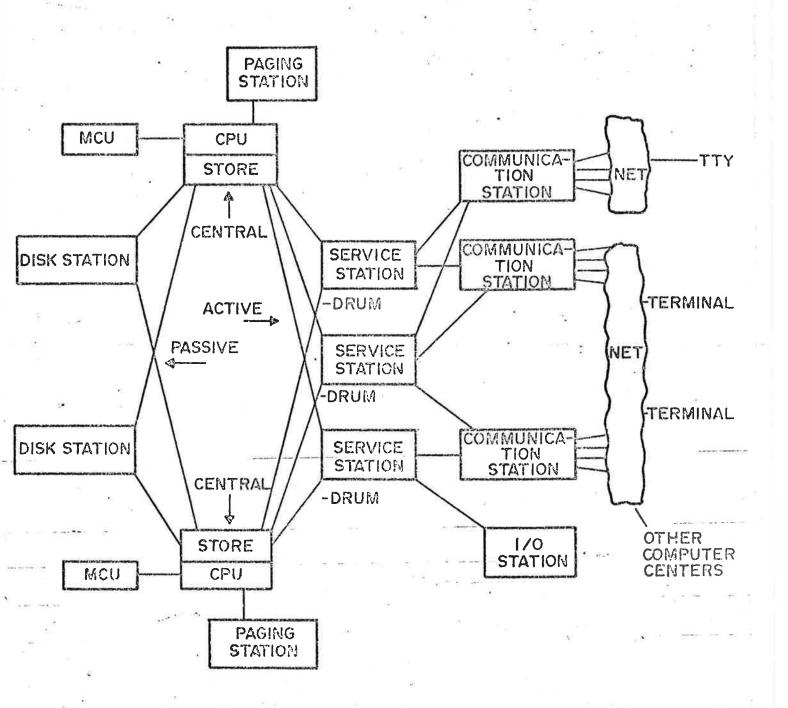

If both computers are identical and perform large amounts of computations, then the system is called a <u>federated or loosely-coupled</u> dual computer system. This configuration is often used in fail safe processor systems. When used as such, the processor-to-processor data link is used for status testing and failure notification.

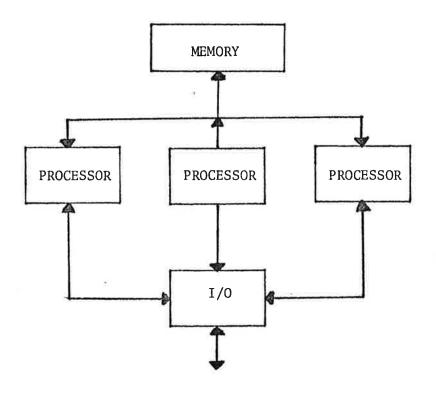

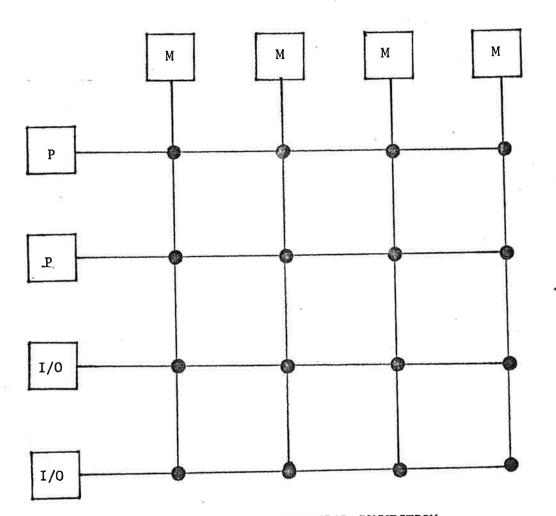

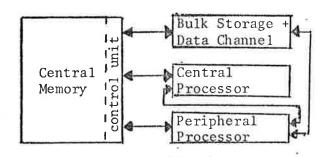

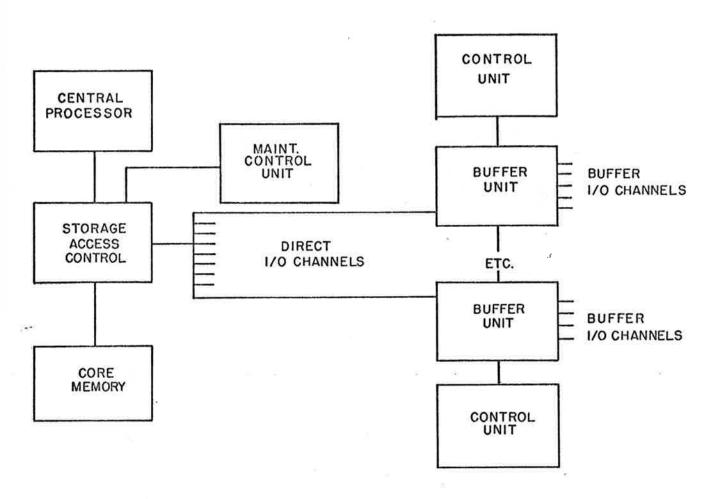

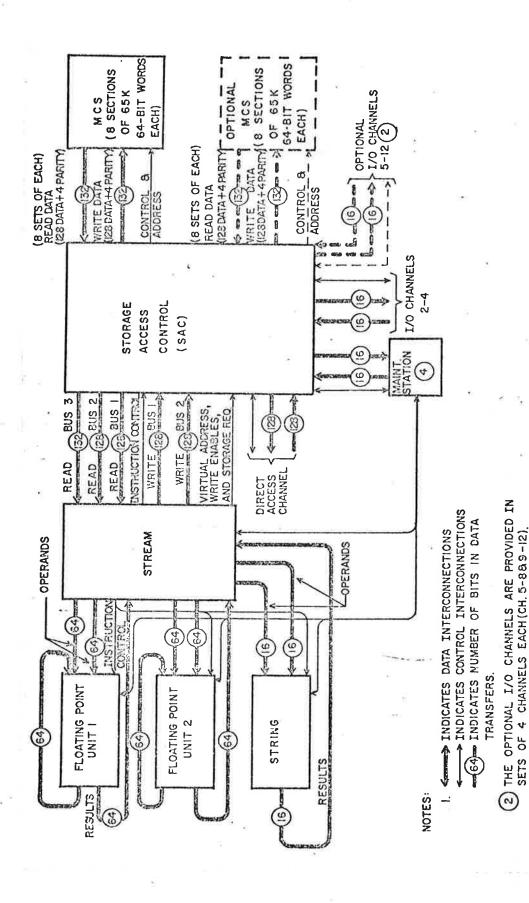

A multiprocessor system configuration is shown in Figure 9.

Both memory and I/O channels are shared by all processors on equal basis. The processors are often identical, however, they need not be. If they are, the operating system assigns tasks to the processors as they become available. Because resources are shared, the operating system must resolve the inevitable conflicts, if the system is to operate. An efficient multiprocessor must minimize the overhead incurred in resolution of these conflicts.

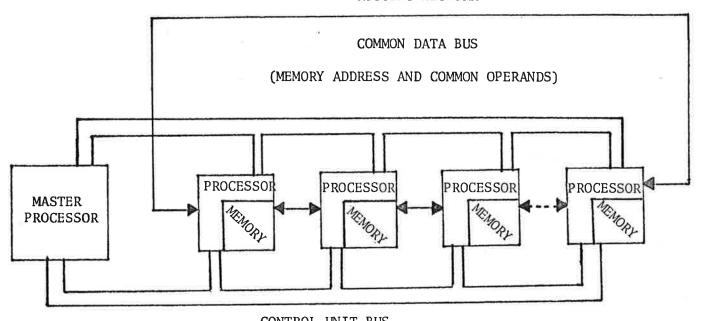

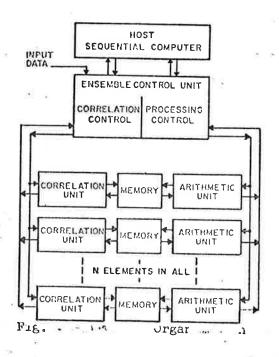

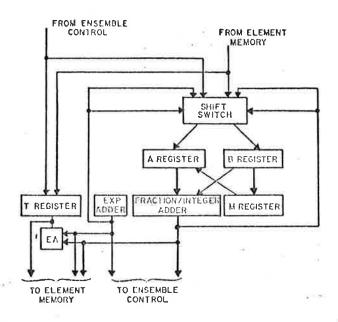

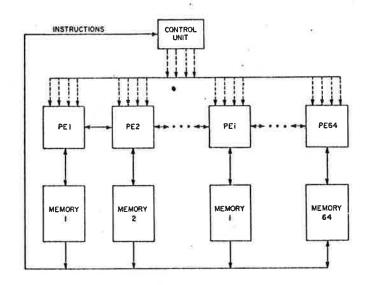

An organization which differs radically from any of those discussed previously is that of the <u>array processor</u> shown in Figure 10. It is composed of N processors, each of which has its own memory and is able to communicate with

MULTIPROCESSOR CONFIGURATION

Figure 9

its nearby neighbors, and a master processor which controls the operation of the system. Data is entered into the individual processor memories from the master processor. The master processor issues the commands that control the operation of the individual processors. Commands are global in nature, i.e., the command calls all processors to perform the same operation. In addition, most parallel processors have a masking capability which allows them to inhibit execution of a global command. This facility allows the processors to perform independent operations. Processors of this type are most effective when performing vector or matrix operations.

## ROUTING NETWORK

CONTROL UNIT BUS

(INSTRUCTIONS AND COMMON OPERANDS)

## ARRAY PROCESSOR CONFIGURATION

## Figure 10

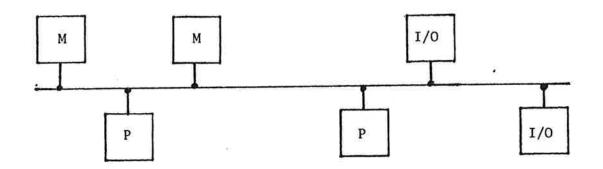

1.4.2 Interconnections. Three interconnection techniques used to tie processors, memories, and I/O processors together are shown in Figures 11 through 13. The simplest of the configurations conceptually is the common data bus shown in Figure 11. All modules are connected in parallel to the common bus. The bus may be a word, byte, or bit wide depending on the desired data transfer rate. Narrower busses require complex control hardware. Access to the bus is granted to processors, one-at-a-time, on a time multiplexed basis. Assuming a fixed memory cycle time, one possible procedure for controlling access is to allow each processor access to the bus on successive memory cycles in a round robin fashion, i.e., P<sub>1</sub>, P<sub>2</sub>, P<sub>3</sub>, P<sub>4</sub>, P P<sub>2</sub> ... etc. If there are N processors then each will be able to access memory once every N memory cycles. Herein, lies the primary disadvantage of the common data bus, i.e., the waiting time for information increases as the number of units on the bus increases. This is offset by the ease with which additional modules may be added to the bus.

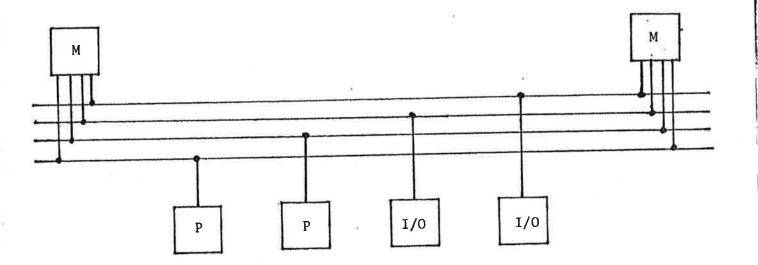

Figures 12 and 13 show two interconnection methods which are essentially the same. The multiport memories allow individual processors to access different memory modules at the same time. This is accomplished by providing multiple inputs to each memory module and separate buses for each processor. A processor's bus connects to one port on each memory module. If more than one processor requests the same memory module, then hardware switching networks within the module resolve the conflict and grant access to only one of the requesting processors. This interconnection method overcomes the data rate limitation of the common bus. However, it has the disadvantage that the number of modules which can be added to the system is limited by the number of parts which were designed into the multiport memory module. The crossbar style interconnection technique overcomes this limitation. The crossbar network is a modular switching network which can grow to accommodate new memory and processor modules. One crosspoint switching network is added for each desired processor to memory data path. A crossbar may be full or partially full depending on the number of desired data paths. The memory modules are single port. Conflicts are resolved within the crosspoint switch in a manner similar to that used in the multiport memory module on a column basis. A variety of conflict resolution techniques is possible.

COMMON DATA BUS

Figure 11

# MULTIPORT MEMORY CONNECTION

Figure 12

CROSSBAR CONNECTION

Figure 13

#### 1.5 COMPUTER SOFTWARE

5

One of the sources of the considerable power inherent in generalpurpose digital computer systems has been the concept of the stored program, it being set forth in virtually its present-day form by von Neumann in 1948 [1]. Then as now, the program was a series of coded instructions stored in the memory of the computer which, when interpreted in sequence, caused the computer to (1) accept data from an outside source, (2) perform calculations on the data, (3) modify its own sequence of operations on the basis of the data, and (4) present data to an outside user. Of these, it is the third--the ability to "interpret" the data and act in various ways depending on the "interpretation" -- that is the key the unique power of the computer system, for with it the computer may assess alternatives and make choices based on complex sets of criteria. This, coupled with the great speed of the hardware, allows the properly programmed computer to accomplish tasks of previously unthinkable complexity.

1.5.1 The Development of Computer Programming. The first computer programs essentially reproduced the patterns which were stored in memory. In the binary machines such as von Neumann's, the entire program could be written as a series of zeros and ones. The octal system of numbers was soon adopted, however, for the representation of addresses and numbers in the computer, and a system of alphabetic characters was used to represent the instruction codes. Programs thus denoted were said to be written in machine language and the coding was said to use absolute addressing.

The difficulty with coding in this way was quickly apparent, for not only was the resultant series of letters and numbers an unnatural form for a man to interpret, it was also almost completely unyielding when it became necessary to make changes or to correct mistakes. The solution was to allow the man to deal in symbols for instructions and addresses and to let the computer itself make the transformation from the symbols to the absolute numbers they represented. The computer program that did this task was called a symbolic assembler; it dealt with programs prepared in assembly language using the technique of symbolic addressing.

The simple assemblers of the late 1950's were gradually extended with the incorporation of <u>pseudo-operations</u> (instructions to the assembler itself rather than parts of the program being assembled), <u>conditional</u> assembly (actions

conditioned on the states of switches, the values of constants, the progress of the assembly, etc.) and in conjunction with appropriate loaders, relocatable routines (ones whose exact locations in core are determined at load time--hence ones which can be easily used as part of many different programs).

The development of <u>macro-assemblers</u> during the 1960's lead to today's very powerful assemblers which provide the skillful programmer with tools with which to write efficient and capable programs to handle the most complex problems. The macro-assembler is able to recognize system and programmer defined <u>macro-instructions</u>, or simply <u>macros</u>, which are names given to certain patterns of coding which are used again and again in the program. The use of these macros made coding easier by reducing the effort needed to write the code, by making the coding less error-prone and by making changes easier to incorporate. Extensions in the form of <u>nested</u> macros, redefinitions within macros and conditional macro expansions made the concept from a coding convenience to a useful and powerful tool.

However, the operative word in the paragraph above as applied to the programmer is "skillful". As the computer systems became larger, faster, more capable, the user of the system found himself less able to cope unless he were a professional programmer—a situation which led to intensive work in two areas: <a href="https://discrete-bigs.ncm/high-order\_languages">high-order\_languages</a> and <a href="https://discrete-bigs.ncm/operating\_systems">operating\_systems</a>. The former were languages intended to allow the non-programmer specialist to write programs for computers without concern for the mass of detail implicit in an assembly language program. On the other hand, operating systems were developed to manage the expensive and complex computer systems so that they might be used in efficient and reasonable ways. After a short look at the subject of data structures encountered in computer applications, we will take a more extensive look at each of these subjects.

1.5.2 <u>Data Structures</u>. It is the nature of the mind to organize facts (data) into structures such that inter-relationships among the facts may become clear and may be dealt with. Computers, being highly organized creations of the minds of men, also deal with data organized in various structures. A goodly part of any computer program, sometimes explicitly and at other times implicitly because of the facilities of the operating system or the programming language, is devoted to matching the structure of the data to the structures of the media on which they are stored.

The structure of a storage medium is frequently described in terms of the order in which its contents may be accessed. Clearly, the most general of all is the so-called random access memory (RAM) where each unit of data has a unique address, for upon this structure may be imposed any more restrictive form. Next, in the usual hierarchy is the block random access memory in which each relatively large collection of data may be accessed without regard to its place among the other blocks, but within the block a second level of addressing is necessary. Many drum memories are organized this way. (Note that if the bit is taken as the unit of information, the usual word or byte addressed memory is in reality block random access, with the word or byte as the block.)

The serial access memory is the last of the three forms usually found in systems today. In this form, epitomized by magnetic tape, access to any unit of information depends on having had access to all its predecessors.

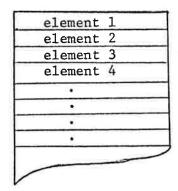

Note that despite the variety of access means, the underlying addressing structure in all these storage types has been one-dimensional. That is, there is a sequence of addresses from beginning to end such that given any address, the next may be calculated by a single elementary operation (e.g., add one). Within this framework, the computer program deals with data arranged in a number of ways, the simplest to handle being the <a href="file">file</a>, a collection of elements either unstructured (random) or sequential. Although random files on sequential storage media have been difficult to deal with, the availability of large-scale random access memories and the simplicity of the file structure have served to make this a rather straightforward case.

The <u>array</u> is an important data structure, especially in science and engineering. A one-dimensional array is called a <u>vector</u> and a two-dimensional array a <u>matrix</u>. Multi-dimensional arrays, though specially named, are also frequently found. One characteristic of array processing is the frequent application of the same operation to all or many members of the array at the same time. A single sequential processor must be programmed to cycle through the array to perform the required calculations—a not inconsequential task.

Other structures frequently found are strings, lists, rings, trees and lattices. A <u>string</u> is a sequence of elements, usually characters, of variable length in which the order of the elements is the important characteristic. This structure is found in situations involving message processing

or other kinds of language interpretation. Those machines with provisions to address and manipulate characters (bytes) and character groups obviously are best suited to these uses.

An ordered sequence of elements each of which contains a pointer to the location of the next item is called a <u>list</u>. Obviously, the successive elements need not be stored in successive locations in memory, but may be scattered throughout. The primary advantage of a list structure is the ease with which the list may be updated. If a new element is to be added between two pre-existing elements, it may be stored at any free location in memory and its pointer set to the location of the successor. The pointer of the predecessor is then set to this location as its new successor.

A list whose last element points back to the first, forming an endless loop, is called a <u>ring</u>.

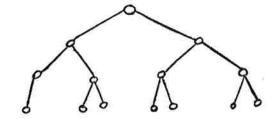

Hierarchical structures are frequently represented as trees. A tree is a two-dimensional structure each of whose elements (except first and last) has exactly one predecessor and one or more successor. The last element of each branch—the one with no successor—is called the <a href="Leaf">Leaf</a> element. If the first element has a predecessor the structure is called a rooted tree, otherwise, <a href="unrooted">unrooted</a>.

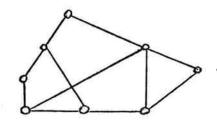

If, in a tree-like structure, each element has more than one predecessor, the whole is called a <u>lattice</u>. The various structures described above are depicted in Figure 1.4.1.

Programming Languages and Applications Programming. As mentioned above, the main impetus for the development of highorder programming languages was the hope that the computer

would be made more approachable by non-programmer professionals

who, after all, were providing the major workload for the

systems. The first of the languages so developed was FORTRAN

(for FORmula TRANslator), intended to allow scientists and

mathematicians to write natural and understandable programs

in what looked like mathematical notation. All of the routine

housekeeping functions as well as input and output were done

by the compiler, based on relatively straightforward standards

and conventions. That FORTRAN is now the most widely used

programming language, and that it even now closely resembles

its original implementation, is a tribute to the great skill

with which it was conceived and executed.

|   | element |

|---|---------|

|   | element |

|   | element |

|   | ( )     |

|   | •       |

|   |         |

|   | •       |

|   | 9.€5    |

|   |         |

| _ |         |

| a) | random | file. |

|----|--------|-------|

## e) string

| element        | 4 | pointer |

|----------------|---|---------|

| <b>element</b> | 1 | pointer |

| element        | 2 | pointer |

| element        | 5 | end     |

| element        | 3 | pointer |

# f) list

h) tree

# b) sequential file

## d) matrix array

| element | 1 | pointer |

|---------|---|---------|

| element | 2 | pointer |

| element | 4 | pointer |

| element | 3 | pointer |

# g) ring

# i) lattice

Figure 1.5.1

REPRESENTATIONS OF DATA TYPES

But good as it was, FORTRAN was not the answer to all of the needs of computer users. In particular, FORTRAN made no provision for data structures other than random files and oneand two-dimensional arrays. Business and financial data processing make wide use of sequential files and of hierarchies of random and sequential files, hence a language providing facilities for the easy use of such structures was called for. COBOL (COmmon Business Oriented Language) was such a language; it also provided facilities not found in FORTRAN for defining business oriented functions.

In 1958, the specifications of what was hoped to be an international standard mathematical language was published as ALGOL 58. Since then, new standard versions have been defined culminating in ALGOL 68 currently being touted. ALGOL is used as the standard language for publication of algorithms and has been widely accepted as a programming language in Europe. It is used to a lesser degree in the United States but some of its derivatives, notably JOVIAL, have achieved some acceptance here.

In order to allow convenient processing of lists, such languages are IPL-V and LISP were developed, and for processing strings and unstructured text, SNOBOL and TRAC, among others, were written. Furthermore, in a veritable explosion of effort, languages have been developed for a vast range of special purposes, using concepts and language peculiar to particular fields from civil engineering to making animated movies. The definitive works on many of these languages have been collected by Rosen [2].

A newer general-purpose language gaining great popularity is the IBM-backed PL/l. This language was developed during the mid-1960's as an extension to and a replacement for FORTRAN. It has capabilities in many areas and could well be a replacement for ALGOL and COBOL, as well as FORTRAN.

When, in the design of a computer system, it becomes necessary to choose the language in which the applications programs of the system are written, great care should be expended to ensure that the one(s) chosen will have the following attributes. The language should match the task—though business systems can and have been coded in FORTRAN, the extra effort hardly justifies the choice. The language should allow natural expression of the data with which the system deals—it may be that a special language, or dialect

of an existing language, should be developed for the application. Finally, the language should impose no arbitrary limits on the development of the system—a built—in maximum array dimension may make a particular algorithm impossible or hard to program, for instance.

1.5.4 Operating Systems. As computer systems increased in size and scope it became clear that major economics would result from letting the computer assist in the sequencing of tasks and in the supplying of services. The earliest systems accepted an input stream pre-stored on tape or from decks of cards and supplied compilers, assemblers, loaders, sort programs, core dump programs, etc. from a system library on magnetic tape. The output was usually stored on tape for later off-line printing and/or punching. Their objective was to speed up operations in the so-called "closed-shop" batch operation.

A parallel development was the building of continuously running real-time systems. These systems were meant to control processes while they were taking place—hence real-time. The command and control systems from SAGE onward are examples of this kind of system.

A number of pivotal concepts have since been incorporated to produce the multi-purpose operating systems of today.

<u>Interrupt processing</u>. The key to real-time operation was the introduction of active interruption of the computer processing by external devices. Multi-level priority schemes allow a variety of fast- and slow-speed devices to be monitored with processing geared to the needs of each.

<u>Multiprogramming</u>. The servicing of slow-speed input/output devices requires only a small fraction of the time available on the computer. To make use of this time, operating systems have been devised which can schedule many tasks at once, working on each in turn while allowing the slow I/O to take place for the others. In this way, expensive equipment can be used to maximum advantage.

Multiprocessing. As the variety of tasks increased, it became apparent that some would require a very large part of the total system while others would require much smaller parts. One way to operate efficiently would be to supply numbers of each of the basic computing resources—computing modules, memory modules, I/O channels, etc.—and to assign these resources on a dynamic basis to the various jobs being run. A machine with multiple computing elements is called a multiprocessor and operating in such a way that a number of tasks are being processed in parallel is called multiprocessing.

Interactive Systems. Since the early days of command/control systems, one aim of system designers has been to build systems with which men could interact on a dynamic basis. Despite great strides, there is still a certain barrier between a human operator and the lightning-fast computer. The work goes on, however, with indications of success with direct voice communication, recognition of handwritten messages, etc.

Time-sharing Systems. The extreme speed of the computers means that a single interactive user is actually using only the merest fraction of the computers power. By using the technique of time-slicing, a single system can be shared by many interactive users, each of whom thinks of himself as the only user: the computer assigns each user a few milliseconds out of each second and rotates its attention among them. With proper hardware and operating system, each user can be assigned enough resources so that it appears that the whole machine is his. By means of the virtual memory concept, a total addressable memory space larger than the main memory of the computer can be assigned to each user. This is because most of the memory actually is stored on mass memory devices outside the machine and only the small part active at any one time is brought into the main memory.

1.5.5 Summary. A very large part of any computer system is the software: the operating system and the application programs. The total cost of this software will usually equal and sometimes may exceed the hardware cost. Modern techniques involving high-order languages and sophisticated operating systems can be used to prepare efficient software in an efficient manner.

## References

- [1] Burks, A.W., Goldstein, H.H., von Neumann, J., "Preliminary discussion of the logical design of an electronic computing instrument", (Part 1, Vol. 1), a report prepared for the U.S. Army Ordnance Dept., 1946 in collected works of John von Neumann, Vol. 5, A.H. Taub (Ed.), MacMillan Co., New York 1963.

- [2] Rosen, S. (ed), <u>Programming Systems and Languages</u>, McGraw-Hill, New York, 1967.

## REFERENCES

- 1. Flores, Ivan, Computer Organization, Prentice-Hall, 1969.

- 2. Flores, Ivan, Data Structures, Prentice-Hall, 1970.

- 3. Stimler, Saul, Real-Time Data Processing Systems, McGraw-Hill, 1969.

- 4. Gear, Computer Organization and Programming, McGraw-Hill, 1969.

- 5. Martin, James, Design of Real-Time Computer Systems, Prentice-Hall, 1967.

- 6. Estrin, G., and Fuller, R., Algorithm for Content-Addressable Memories, Proceedings IEEE, pp. 118-130, Pacific Computer Conf., 1963.

- 7. Ewing, R.G., and Davies, P.M., An Associative Parallel Processor with Applications to Picture Processing, Proc. FJCC, pp. 105-115, 1965.

- 8. McKeever, B.T., The Associative Memory Structure, Proc. FJCC, pp. 371-388, 1965.

- 9. Flynn, M.J., Very High Speed Computing Systems, Proc. IEEE, Vol. 54, No. 12, pp. 190-1909, Dec. 1966.

- 10. Lewin, M.H., Retrieval of Ordered Lists from A Content Addressed Memory, RCA Review, June 1962, pp. 215-229.

- Kautz, W.H., An Augmented Content-Addressed Memory Array for Implementation with Large-Scale Integration, <u>J.A.C.M.</u>, Vol. 18, No. 1, Jan. 1971.

- 12. Wald, L.D., An Associative Memory Using Large-Scale Integration, NAECON 70 Record, pp. 277-281.

- 13. Engles, R.W., Concepts and Terminology for Programmers, IBM TR 00.1663, October 2, 1967.

- 14. Lyons, R.E., The Application of Associative Processing to Automated Air Traffic Control, A White Paper submitted to the FAA, Feb. 14, 1969.

- 15. Cannel, M.H., et.al., <u>Concepts and Applications of Computerized Associative Processing</u>, MTR-1735, MTR-863, ESD-TR-70-379.

- 16. Thurber, K., The Application of Parallel Processing Techniques To Air Traffic Control, Proprietary Report submitted to the FAA, March 16, 1970 by <u>Honeywell Systems and Research Center</u>.

- 17. Meilander, et.al., Applicability of Parallel Processing Techniques for ATC System Modernization, <u>Final Report</u> submitted to the FAA Feb. 24, 1970 by the <u>Goodyear Aerospace Corp</u>.

## 2.0 ATC DATA PROCESSING REQUIREMENTS

#### 2.1 INTRODUCTION

In this chapter we will discuss three aspects of the ATC system evaluation process. In the first section, we discuss the recent efforts to predict the size of the computing facility needed to carry out the ATC functions in the 1980's. We do this by considering the estimations of traffic levels, by considering the effects of increased traffic on the data processing loads and finally by looking at the estimations made of the size of the data processing system needed to do 1980 ATC.

The second section will be devoted to a general assessment of the near future development of air traffic control systems in terms of the hardware and software and their interactions. Large capacity and high reliability are the characteristics stressed and developments which lead in their direction are discussed.

The third section is devoted to the evaluation techniques to be applied to ATC systems. A description of evaluation measures is followed by a discussion of the way these measures are applied in system design and evaluation and to the approaches used to develop these measures.

Finally, a few conclusions are drawn concerning profitable directions for future efforts in ATC system design and evaluation.

## 2.2 ESTIMATIONS OF ATC DATA PROCESSING LOADS FOR 1980

2.2.1 Estimations of Traffic Levels. Probably the best and most recent forecast of air traffic levels currently available is that done by the working group (Group IV) on users needs for the DOT Air Traffic Control Advisory Committee (ATCAC) and reported by Ashby [1,2]. Their estimates were derived by collecting from the FAA and others [see e.g. 3-6] counts of numbers of types of aircraft and their utilizations in hours for the then most recent year [1968] and forecasts of the same numbers for the years 1980 and 1995. The basic data used by the group in deriving their estimates are probably as good as can be obtained; that is not to say, however, that the data base was entirely adequate, as pointed out by Ashby, himself. [1, p. 469]